集成電路設計 數字世界的基石

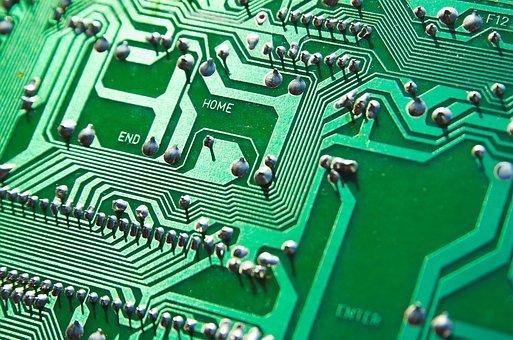

在當今這個高度數字化的時代,集成電路(Integrated Circuit, IC)早已無處不在,它是智能手機、計算機、汽車乃至無數智能設備的“心臟”。而集成電路設計,作為整個IC產業鏈的源頭和核心,是決定芯片性能、功耗、成本與創新速度的關鍵環節。

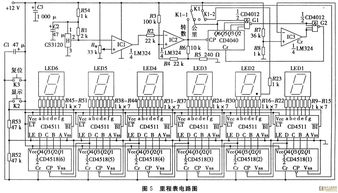

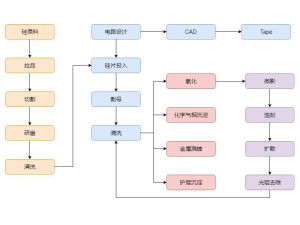

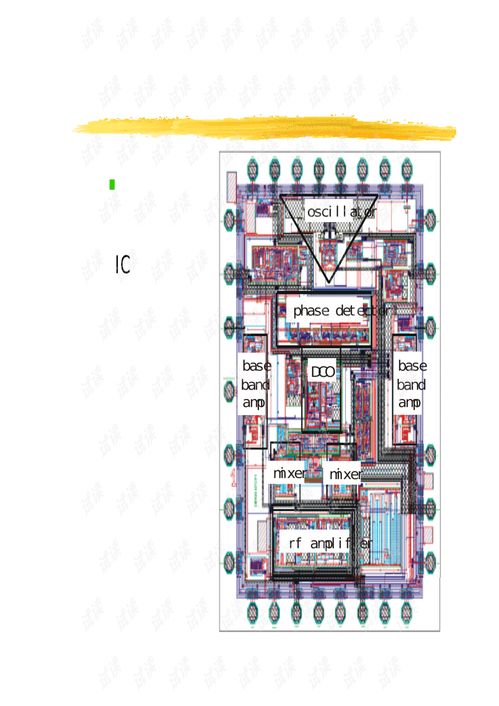

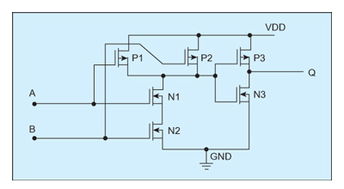

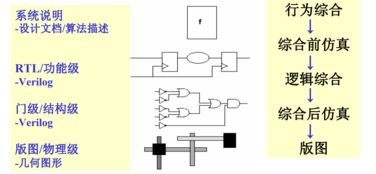

集成電路設計,簡而言之,是將系統、邏輯與性能的設計要求轉化為物理版圖的過程。這是一個極其復雜且多層次的工程領域,通常遵循一套標準化的設計流程。流程始于系統架構定義,設計者需要明確芯片的功能、性能指標(如處理速度、功耗預算)以及目標應用場景。緊接著是前端設計,包括使用硬件描述語言(如Verilog或VHDL)進行邏輯設計、功能仿真和綜合,將高級描述轉化為門級網表。后端設計則涉及物理實現,如布局規劃、時鐘樹綜合、布線、物理驗證和版圖生成,最終輸出可供晶圓廠制造的GDSII文件。

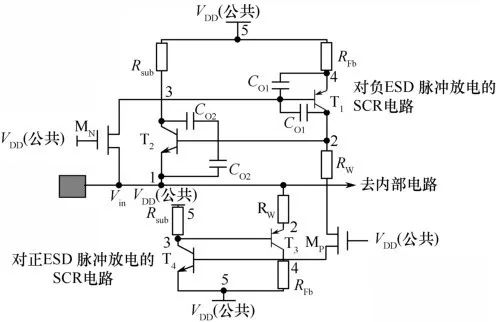

隨著半導體工藝節點不斷微縮至納米甚至更小尺度,集成電路設計面臨著前所未有的挑戰。物理效應日益顯著,如寄生效應、工藝變異和量子隧穿效應,使得設計的可預測性和穩定性變差。功耗問題,尤其是靜態功耗(漏電功耗),已成為高性能芯片設計的瓶頸,“功耗墻”問題亟待解決。設計復雜度的爆炸式增長,一個先進芯片可能集成數百億個晶體管,這要求設計工具、方法和團隊協作模式的持續革新。

為了應對這些挑戰,集成電路設計領域也在不斷創新。電子設計自動化(EDA)工具是設計師的“左膀右臂”,它們通過更強大的算法和人工智能技術,幫助進行更精準的仿真、優化和驗證。新的設計方法學,如基于平臺的設計、可重用IP核以及芯片堆疊(3D-IC)技術,正被廣泛采用以提高設計效率并實現更優的系統性能。針對特定領域(如人工智能、自動駕駛)的定制化芯片(ASIC)和可編程邏輯器件(FPGA)的設計,也開辟了新的賽道。

集成電路設計將繼續沿著更高性能、更低功耗、更強集成度和更短設計周期的方向發展。它不僅是技術進步的引擎,更是國家科技實力和產業競爭力的重要體現。從概念到硅片,集成電路設計師們用智慧與汗水,在方寸之間構建著支撐數字世界的微觀宇宙。

如若轉載,請注明出處:http://www.keydot.com.cn/product/71.html

更新時間:2026-03-15 21:42:13