專用集成電路設計 精準定制的技術基石

在當今信息技術飛速發展的時代,集成電路(IC)作為電子設備的心臟,其重要性不言而喻。其中,專用集成電路(ASIC,Application-Specific Integrated Circuit)設計,更是代表了集成電路領域內深度定制與高性能的尖端方向。與通用處理器(如CPU、GPU)不同,ASIC是為特定應用、特定算法或特定客戶需求而量身定制的芯片。它通過犧牲通用性,在目標領域內實現了無與倫比的性能、能效和成本優勢。

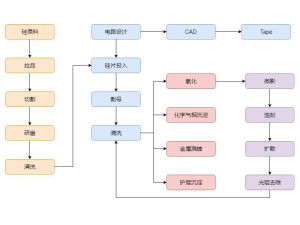

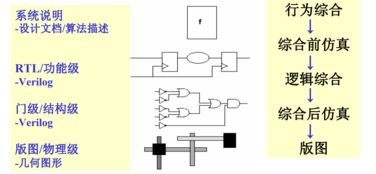

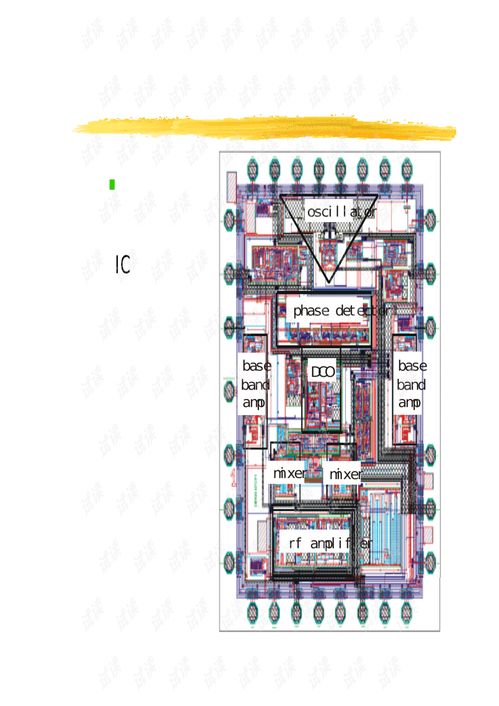

ASIC設計的核心流程是一個復雜而嚴謹的系統工程。它通常始于明確的設計需求與系統架構規劃。設計團隊需要與客戶或系統工程師緊密合作,將功能、性能、功耗、面積和成本等指標轉化為具體的電路架構方案。隨后進入關鍵的硬件描述語言(如Verilog或VHDL)編碼階段,即通過代碼來“描述”芯片的邏輯功能。

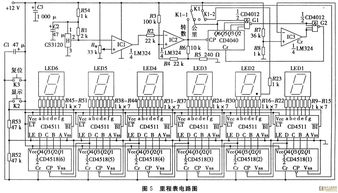

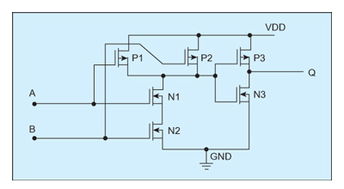

邏輯設計完成后,需要通過功能仿真進行驗證,確保其行為符合預期。之后便是綜合環節,將高級的硬件描述代碼轉換為由基本邏輯門(如與門、或門)組成的網表。這標志著設計從行為級進入到了門級。

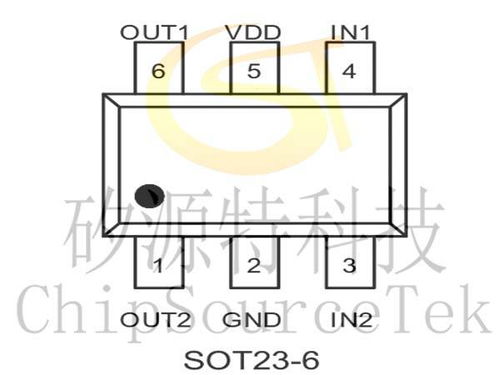

物理設計是ASIC流程中極具挑戰性的一步。它包括布局(將邏輯單元放置在芯片版圖上)、布線(用金屬線連接這些單元)、時鐘樹綜合(確保時鐘信號同步到達各個單元)以及功耗和信號完整性分析。每一步都需要借助強大的電子設計自動化(EDA)工具,并反復迭代優化,以在性能、功耗和面積之間取得最佳平衡。

經過嚴格的驗證和簽核,設計數據將以GDSII等標準格式交付給晶圓廠進行流片制造。一顆ASIC從設計到量產,往往需要數月甚至數年的時間,并投入巨大的研發成本。因此,其應用場景通常集中在需求量足夠大、或者對性能功耗有極致要求的領域。

目前,ASIC已經滲透到我們數字生活的方方面面。最典型的例子是智能手機中的基帶處理器、圖像信號處理器(ISP)以及人工智能加速單元(NPU)。在數據中心,谷歌的TPU(張量處理單元)是專為機器學習定制的ASIC,極大地提升了AI訓練和推理的效率。比特幣礦機、汽車自動駕駛系統、高端網絡路由器和各類工業控制設備中,也隨處可見ASIC的身影。

隨著5G、人工智能、物聯網和自動駕駛的蓬勃發展,市場對計算效率的要求將越來越高。ASIC憑借其“專芯專用”的特性,必將在這些高增長領域扮演愈發關鍵的角色。先進工藝節點(如3納米、2納米)的演進、Chiplet(芯粒)異構集成技術的成熟,以及EDA工具的持續智能化,也將推動ASIC設計方法學不斷革新,在追求更高性能、更低功耗的道路上持續突破,繼續夯實其作為現代信息技術基石的牢固地位。

如若轉載,請注明出處:http://www.keydot.com.cn/product/70.html

更新時間:2026-03-15 01:56:11