集成電路可靠性設(shè)計(jì) 從理念到實(shí)踐的全面解析

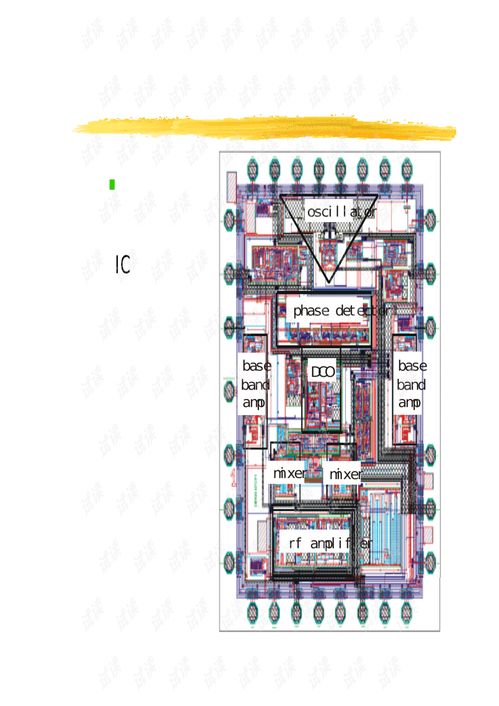

在現(xiàn)代電子工業(yè)中,集成電路(IC)作為信息技術(shù)的核心基石,其性能與可靠性直接決定了電子設(shè)備的穩(wěn)定性和壽命。隨著工藝節(jié)點(diǎn)的不斷縮小、芯片集成度的持續(xù)飆升以及應(yīng)用場景的日益嚴(yán)苛(如汽車電子、工業(yè)控制、航空航天等),傳統(tǒng)的設(shè)計(jì)-制造-測試模式已不足以應(yīng)對(duì)復(fù)雜系統(tǒng)的可靠性挑戰(zhàn)。因此,可靠性設(shè)計(jì)已成為集成電路設(shè)計(jì)流程中不可或缺、甚至需要前置的關(guān)鍵環(huán)節(jié)。它并非單一技術(shù),而是一套貫穿芯片整個(gè)生命周期的系統(tǒng)性方法論,旨在從設(shè)計(jì)源頭預(yù)防、控制并緩解失效風(fēng)險(xiǎn)。

一、可靠性設(shè)計(jì)的核心理念與重要性

可靠性設(shè)計(jì)的核心目標(biāo)是確保芯片在其規(guī)定的壽命周期內(nèi),在預(yù)期的使用環(huán)境和工作條件下,能夠穩(wěn)定、無誤地執(zhí)行預(yù)定功能。它與功能設(shè)計(jì)、性能設(shè)計(jì)、功耗設(shè)計(jì)并列為芯片設(shè)計(jì)的四大支柱。其重要性體現(xiàn)在:

- 經(jīng)濟(jì)性與市場競爭力:早期發(fā)現(xiàn)并解決可靠性問題,能極大降低后期測試、返工、維修乃至召回的成本。一顆高可靠的芯片是贏得高端市場(如車規(guī)級(jí)、軍工級(jí))信任的通行證。

- 系統(tǒng)安全與法律責(zé)任:在自動(dòng)駕駛、醫(yī)療設(shè)備等安全攸關(guān)領(lǐng)域,芯片的微小失效可能導(dǎo)致災(zāi)難性后果,并帶來嚴(yán)峻的法律責(zé)任。

- 技術(shù)發(fā)展的必然要求:先進(jìn)工藝(如FinFET、GAA)在帶來性能提升的也引入了新的可靠性威脅(如柵氧經(jīng)時(shí)擊穿、熱載流子注入、負(fù)偏壓溫度不穩(wěn)定性等),必須在設(shè)計(jì)階段加以應(yīng)對(duì)。

二、主要可靠性失效機(jī)理與設(shè)計(jì)應(yīng)對(duì)策略

可靠性設(shè)計(jì)需針對(duì)特定的物理失效機(jī)理,采取相應(yīng)的設(shè)計(jì)加固措施:

- 電遷移:在高電流密度下,金屬互連線中的原子被電子“吹走”,導(dǎo)致導(dǎo)線開路或短路。

- 設(shè)計(jì)策略:遵守更嚴(yán)格的布線規(guī)則,使用更寬的導(dǎo)線,增加通孔/接觸孔數(shù)量,采用銅互連及阻擋層材料,在電路設(shè)計(jì)中避免持續(xù)大電流路徑。

- 熱載流子注入:高電場下的載流子獲得足夠能量注入柵氧化層,造成器件參數(shù)(如閾值電壓)漂移。

- 設(shè)計(jì)策略:優(yōu)化器件尺寸和偏置電壓,避免晶體管工作在接近擊穿電壓的區(qū)域;采用抗HCI的器件結(jié)構(gòu)或工藝。

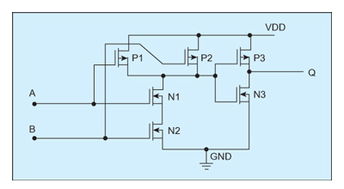

- 負(fù)偏壓溫度不穩(wěn)定性:主要在PMOS管中,在負(fù)柵壓和高溫下,界面陷阱產(chǎn)生導(dǎo)致閾值電壓絕對(duì)值升高,驅(qū)動(dòng)能力下降。

- 設(shè)計(jì)策略:優(yōu)化工藝以改善柵氧界面質(zhì)量;在電路設(shè)計(jì)時(shí)考慮NBTI導(dǎo)致的性能退化余量(設(shè)計(jì)裕度);采用動(dòng)態(tài)偏置或恢復(fù)技術(shù)。

- 經(jīng)時(shí)擊穿:柵氧化層在長期電場應(yīng)力下累積損傷,最終導(dǎo)致絕緣失效。

- 設(shè)計(jì)策略:使用更厚或更高質(zhì)量的柵氧(在性能與可靠性間權(quán)衡);嚴(yán)格控制工作電壓;采用電壓域設(shè)計(jì)和電源管理技術(shù)。

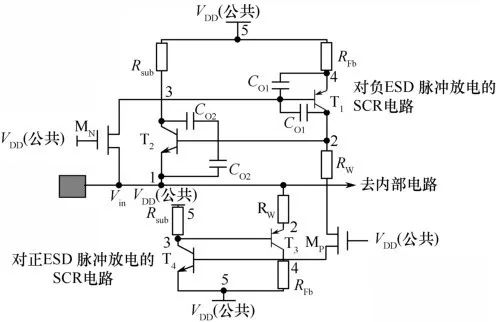

- 靜電放電與閂鎖效應(yīng):外部靜電或內(nèi)部噪聲可能引發(fā)瞬間大電流,損壞電路或觸發(fā)寄生可控硅結(jié)構(gòu)導(dǎo)致閂鎖。

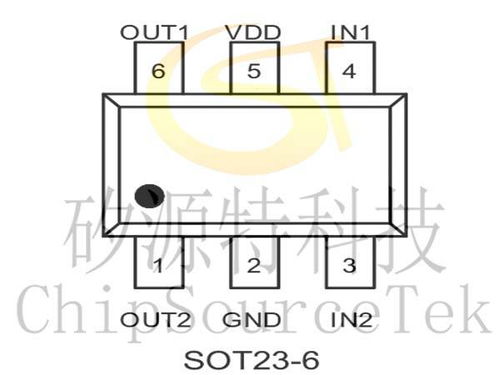

- 設(shè)計(jì)策略:在芯片所有I/O端口及敏感內(nèi)部節(jié)點(diǎn)設(shè)計(jì)完整的ESD保護(hù)電路(如GGNMOS、RC觸發(fā)SCR等);通過良好的版圖布局(增加保護(hù)環(huán)、增大間距)來抑制閂鎖效應(yīng)。

- 軟錯(cuò)誤:由高能粒子(如阿爾法粒子、中子)撞擊引發(fā),導(dǎo)致存儲(chǔ)單元狀態(tài)翻轉(zhuǎn)或組合邏輯瞬時(shí)錯(cuò)誤。

- 設(shè)計(jì)策略:對(duì)關(guān)鍵存儲(chǔ)器采用糾錯(cuò)碼(ECC)、奇偶校驗(yàn);對(duì)觸發(fā)器采用加固單元(如DICE單元);系統(tǒng)級(jí)采用三模冗余等容錯(cuò)設(shè)計(jì)。

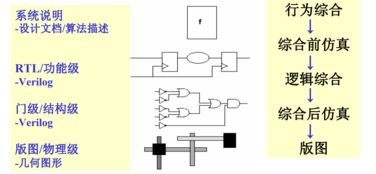

三、可靠性設(shè)計(jì)流程與方法學(xué)

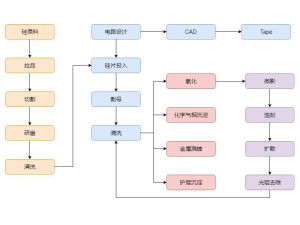

一個(gè)系統(tǒng)的可靠性設(shè)計(jì)流程應(yīng)融入標(biāo)準(zhǔn)的設(shè)計(jì)周期:

- 可靠性目標(biāo)與規(guī)范制定:根據(jù)產(chǎn)品應(yīng)用場景(消費(fèi)級(jí)、工業(yè)級(jí)、車規(guī)級(jí)),明確具體的可靠性指標(biāo)(如FIT率、工作壽命、環(huán)境耐受等級(jí))。

- 設(shè)計(jì)階段的分析與加固:

- 可靠性仿真與預(yù)測:使用專用EDA工具,在電路仿真階段就模擬電遷移、HCI、NBTI等效應(yīng),預(yù)測電路壽命和參數(shù)漂移。

- 設(shè)計(jì)裕度:在時(shí)序、功耗、驅(qū)動(dòng)能力等方面預(yù)留足夠余量,以抵消老化帶來的性能衰減。

- 容錯(cuò)與自修復(fù)設(shè)計(jì):對(duì)于極高可靠要求的系統(tǒng),采用冗余設(shè)計(jì)、自檢電路、可重構(gòu)邏輯等。

- 可測試性設(shè)計(jì):集成用于監(jiān)測老化、溫度和電壓的傳感器,以及用于測試內(nèi)部可靠性的專用電路(如BIST)。

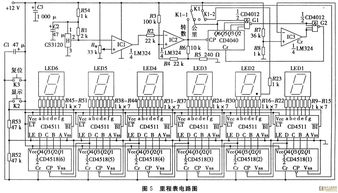

- 版圖階段的可靠性考量:

- 遵守可靠性設(shè)計(jì)規(guī)則:比基礎(chǔ)DRC更嚴(yán)格的間距、寬度規(guī)則,以應(yīng)對(duì)電遷移和自熱效應(yīng)。

- 均勻性與對(duì)稱性:確保電源/地網(wǎng)絡(luò)分布均勻,避免熱點(diǎn);差分對(duì)等關(guān)鍵電路嚴(yán)格對(duì)稱。

- 抗干擾布局:模擬與數(shù)字電路隔離,敏感信號(hào)屏蔽。

- 驗(yàn)證與評(píng)估:

- 可靠性專項(xiàng)驗(yàn)證:檢查ESD保護(hù)網(wǎng)絡(luò)、閂鎖防護(hù)是否完整。

- 老化仿真與壽命評(píng)估:通過仿真數(shù)據(jù),結(jié)合工藝模型,給出芯片的預(yù)計(jì)壽命。

- 制造、測試與監(jiān)控:與制造廠合作,監(jiān)控工藝波動(dòng)對(duì)可靠性的影響;進(jìn)行加速壽命測試,收集實(shí)際數(shù)據(jù)以校準(zhǔn)模型。

四、挑戰(zhàn)與未來趨勢

面向集成電路可靠性設(shè)計(jì)面臨諸多挑戰(zhàn):

- 先進(jìn)工藝的復(fù)雜性:3D集成、異質(zhì)集成、原子級(jí)尺度器件帶來新的、耦合的失效機(jī)理。

- 新材料的引入:高k金屬柵、二維材料、新型互連材料的可靠性數(shù)據(jù)庫和模型尚不完善。

- 系統(tǒng)級(jí)復(fù)雜性:芯片-封裝-系統(tǒng)協(xié)同設(shè)計(jì)與協(xié)同失效分析難度激增。

未來趨勢將聚焦于:

- 設(shè)計(jì)-工藝協(xié)同優(yōu)化:更早、更緊密地與制造端合作。

- 基于機(jī)器學(xué)習(xí)的預(yù)測:利用大數(shù)據(jù)和AI技術(shù),更精準(zhǔn)地預(yù)測芯片壽命和失效點(diǎn)。

- 智能自愈與自適應(yīng)系統(tǒng):芯片能夠?qū)崟r(shí)監(jiān)測自身健康狀態(tài),并動(dòng)態(tài)調(diào)整工作點(diǎn)或啟用備份資源。

- 可靠性標(biāo)準(zhǔn)與IP化:形成更完善的可靠性設(shè)計(jì)標(biāo)準(zhǔn)庫和可復(fù)用的可靠性IP,提升設(shè)計(jì)效率。

###

總而言之,集成電路可靠性設(shè)計(jì)是一個(gè)多學(xué)科交叉、貫穿始終的復(fù)雜工程。它要求設(shè)計(jì)師不僅精通電路與系統(tǒng)知識(shí),還需深刻理解半導(dǎo)體物理、材料科學(xué)和失效機(jī)理。在“后摩爾時(shí)代”,當(dāng)純粹的性能提升愈發(fā)困難,可靠性將成為衡量芯片價(jià)值和競爭力的最關(guān)鍵維度之一。從設(shè)計(jì)伊始就將可靠性內(nèi)植于芯片基因,是打造成功產(chǎn)品、贏得長遠(yuǎn)市場的必由之路。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.keydot.com.cn/product/69.html

更新時(shí)間:2026-03-15 22:06:48